AMD Family 10h Processor BKDG

# BIOS and Kernel Developer's Guide (BKDG) For AMD Family 10h Processors

#### © 2005–2009 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD Arrow logo, 3DNow!, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

MMX is a trademark of Intel Corporation.

Microsoft is a registered trademark of Microsoft Corporation.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Table of Contents**

| 1   | Overview                                                 | 18   |

|-----|----------------------------------------------------------|------|

| 1.  | Intended Audience                                        | 18   |

| 1.2 | 2 Reference Documents                                    | 18   |

| 1.  | 3 Conventions                                            | 19   |

|     | 1.3.1 Numbering                                          |      |

|     | 1.3.2 Arithmetic And Logical Operators                   | 19   |

| 1.4 |                                                          |      |

| 1.  |                                                          |      |

|     | 1.5.1 Revision Conventions                               |      |

|     | 1.5.2 Major Changes Relative to Family 0Fh Processors    |      |

|     | 1.5.3 Changes For Revision C                             |      |

|     | 1.5.4 Supported Feature Variations                       |      |

| 2   | Functional Description                                   |      |

| 2.  | -                                                        |      |

| 2.  |                                                          |      |

| 2.1 | ·                                                        |      |

| 2.2 |                                                          |      |

| ۷., | 2.3.1       BSP initialization                           |      |

|     |                                                          |      |

|     |                                                          |      |

|     | b $b$ $b$                                                |      |

|     |                                                          |      |

|     | 2.3.5 BIOS Requirements For 64-Bit Operation             |      |

|     | 2.3.6 SLIT and SRAT                                      |      |

|     | 2.3.6.1 SLIT                                             |      |

| 2   | 2.3.6.2 SRAT                                             |      |

| 2.4 | $\partial$                                               |      |

|     | 2.4.1 Processor Power Planes And Voltage Control         |      |

|     | 2.4.1.1 VID Pins And Interface Selection                 |      |

|     | 2.4.1.2 Internal VID Registers                           |      |

|     | 2.4.1.3 MinVid and MaxVid Check                          |      |

|     | 2.4.1.4 PSI_L                                            |      |

|     | 2.4.1.5 VID Encodings                                    |      |

|     | 2.4.1.5.1 Boot VID Encodings                             |      |

|     | 2.4.1.5.2 Parallel VID Interface (PVI) Encodings         |      |

|     | 2.4.1.5.3 Serial VID (SVI) Encodings                     |      |

|     | 2.4.1.6 BIOS Requirements for Power Plane Initialization |      |

|     | 2.4.1.7 Hardware-Initiated Voltage Transitions           |      |

|     | 2.4.1.8 Software-Initiated Voltage Transitions           |      |

|     | 2.4.1.8.1 Software-Initiated NB Voltage Transitions      |      |

|     | 2.4.1.8.2 Software-Initiated CPU Voltage Transitions     |      |

|     | 2.4.1.9 SVI Protocol                                     |      |

|     | 2.4.2 P-states                                           |      |

|     | 2.4.2.1 Core P-states                                    |      |

|     | 2.4.2.1.1 Core P-state Control                           |      |

|     | 2.4.2.2 P-state Limits                                   |      |

|     | 2.4.2.3 P-state Bandwidth Requirements                   | . 42 |

|     | 2.4   |         |         | Transition Behavior                                                    |      |

|-----|-------|---------|---------|------------------------------------------------------------------------|------|

|     | 2.4   | .2.5 1  | BIOS    | Requirements for P-State Initialization and Transitions                | . 43 |

|     | 2.4   |         |         | Configuration for Dual-plane Only Support                              |      |

|     | 2.4   | .2.7 1  |         | Northbridge COF and VID Configuration                                  |      |

|     |       | 2.4.2.7 | 7.1     | BIOS NB COF and VID Configuration for SVI and Single-Plane PVI Systems | s.   |

|     |       |         |         | 45                                                                     |      |

|     |       | 2.4.2.7 |         | BIOS NB COF and VID Configuration for Dual-Plane PVI Systems           |      |

|     |       |         |         | sor-Systemboard Power Removal Check                                    |      |

|     |       |         |         | sor-Systemboard Power Delivery Compatibility Check                     |      |

|     | 2.4   |         |         | -Frequency and Power P-State Configuration                             |      |

|     |       | 2.4.2.1 |         | Mixed Power P-State Configuration Sequence                             |      |

|     |       | 2.4.2.1 |         | Mixed Frequency and Power P-State Configuration Rules                  |      |

|     | 2.4   | 2.4.2.1 |         | Mixed Frequency and Power P-State Configuration Sequence               |      |

|     | 2.4   |         |         | Processor P-State Objects                                              |      |

|     |       |         |         | _PCT (Performance Control)                                             |      |

|     |       |         |         | _PSS (Performance Supported States)                                    |      |

|     |       | 2.4.2.1 |         | _PPC (Performance Present Capabilities)                                |      |

|     |       | 2.4.2.1 |         | _PSD (P-State Dependency)                                              |      |

|     | 2.4   | 2.4.2.1 |         | Fixed ACPI Description Table (FADT) Entries                            |      |

|     |       |         |         | (Microsoft® Extended PSS) Object                                       |      |

|     | 2.4   | 2.4.2.1 |         | COF and VID Requirements After Warm Reset                              |      |

|     |       | 2.4.2.1 |         | Core Maximum P-State Transition Sequence After Warm Reset              |      |

|     |       | 2.4.2.1 |         | Core Minimum P-State Transition Sequence After Warm Reset              |      |

|     | 2.4.3 |         |         |                                                                        |      |

|     |       |         |         | hanced State (C1E)                                                     |      |

|     | 2.4   | 2.4.3.1 |         | SMI Initiated C1E                                                      |      |

|     |       |         |         | BIOS Requirements to Initialize SMI Initiated C1E                      |      |

|     |       |         | 4.3.1.2 | •                                                                      |      |

|     | 2.4   |         |         | Flush On Halt                                                          |      |

|     | 2.4.4 |         |         | nd to RAM State (S3).                                                  |      |

| 2.5 |       |         | -       | ansition Sequences                                                     |      |

|     | 2.5.1 |         |         | State Transitions                                                      |      |

| 2.6 | The I |         |         | NB)                                                                    |      |

|     | 2.6.1 |         |         |                                                                        | 63   |

|     | 2.6.2 | The G.  | ART.    |                                                                        | 63   |

|     | 2.6.3 | DMA     | Exclus  | sion Vectors (DEV)                                                     | 64   |

|     | 2.6.4 | Northb  | oridge  | Routing                                                                | 64   |

|     | 2.6   | .4.1    | Addres  | ss Space Routing                                                       | . 64 |

|     |       | 2.6.4.1 | .1      | DRAM and MMIO Memory Space                                             | . 64 |

|     |       | 2.6.4.1 | .2      | IO Space                                                               | . 65 |

|     |       | 2.6.4.1 |         | Configuration Space                                                    |      |

|     | 2.6   |         |         | Transport <sup>™</sup> Technology Routing                              |      |

|     |       | 2.6.4.2 |         | Routing Table Configuration                                            |      |

|     |       | 2.6.4.2 |         | BIOS Requirements for Systems with Mixed Processor Families            |      |

|     |       | 2.6.4.2 |         | Link Traffic Distribution                                              |      |

|     |       | 2.6.4.2 |         | Display Refresh And IFCM                                               |      |

|     | 2.6.5 |         |         | Cache (L3)                                                             |      |

|     | 2.6.6 |         | •       | ubbers                                                                 |      |

|     | 2.6.7 | Physic  | al Add  | lress Space                                                            | 68   |

|     | 2.6.8  |              | lress Map                                                            |     |

|-----|--------|--------------|----------------------------------------------------------------------|-----|

| 2.7 | Links  |              |                                                                      |     |

|     | 2.7.1  |              | ization                                                              |     |

|     | 2.7    |              | ing And Unganging                                                    |     |

|     |        |              | ing Detection And Control                                            | 69  |

|     | 2.7    | .1.3 Link    | Type Detect                                                          |     |

|     |        | 2.7.1.3.1    | Unused Links                                                         |     |

|     | 2.7    | .1.4 Legal   | Topologies                                                           | 69  |

|     | 2.7.2  |              | n and Compensation                                                   |     |

|     | 2.7.3  | Equalization | n                                                                    | 70  |

|     | 2.7.4  | Link Bandv   | vidth Requirements                                                   | 70  |

|     | 2.7.5  | Link Retry   |                                                                      | 71  |

|     | 2.7.6  | Link LDTS    | TOP_L Disconnect-Reconnect                                           | 71  |

|     | 2.7.7  | LDTSTOP      | Requirements                                                         | 71  |

|     | 2.7.8  | Response C   | Ordering                                                             | 72  |

|     | 2.7.9  | Link Testin  | g, BIST, and ILM                                                     | 72  |

|     | 2.7.10 |              | bus Behaviors and Requirements                                       |     |

| 2.8 | DRA    |              | rs (DCTs).                                                           |     |

|     | 2.8.1  |              | guration Registers                                                   |     |

|     | 2.8.2  |              | Multiple Unbuffered Logical DIMMs                                    |     |

|     | 2.8.3  | ~ ~          | h                                                                    |     |

|     | 2.8.4  |              | Unganged Mode Considerations                                         |     |

|     | 2.8.5  |              | AM Requests                                                          |     |

|     | 2.8.6  | ÷            | ntroller Direct Response Mode                                        |     |

|     | 2.8.7  |              | a Burst Mapping                                                      |     |

|     | 2.8.8  |              | M Initialization                                                     |     |

|     | 2.8    |              | nd Controller Mode Configuration                                     |     |

|     |        |              | ompensation initialization                                           |     |

|     |        |              | ROM-Based Configuration                                              |     |

|     |        |              | SPD ROM-Based Configuration                                          |     |

|     |        | 2.8.8.4.1    | Trdrd (Read to Read Timing)                                          |     |

|     |        | 2.8.8.4.2    | Twrwr (Write to Write Timing)                                        |     |

|     |        | 2.8.8.4.3    | Twrrd (Write to Read DIMM Termination Turn-around)                   |     |

|     |        | 2.8.8.4.4    | TrwtTO (Read-to-Write Turnaround for Data, DQS Contention)           |     |

|     |        | 2.8.8.4.5    | TrwtWB (Read-to-Write Turnaround for Opportunistic Write Bursting) . |     |

|     |        | 2.8.8.4.6    | FourActWindow (Four Bank Activate Window or tFAW)                    |     |

|     |        | 2.8.8.4.7    | DRAM ODT Control                                                     |     |

|     |        | 2.8.8.4.8    | DRAM Address Timing and Output Driver Compensation Control           |     |

|     | 2.8    |              | M Device and Controller Initialization                               |     |

|     | 2.0    | 2.8.8.5.1    | Software DDR2 Device Initialization                                  |     |

|     |        | 2.8.8.5.2    | Software DDR3 Device Initialization                                  |     |

|     |        | 2.8.8.5.     |                                                                      |     |

|     | 2.8    |              | Sence programming                                                    |     |

|     | 2.8    | -            | M Channel Frequency Change                                           |     |

|     |        |              | M Training                                                           |     |

|     | 2.0    | 2.8.8.8.1    | Write Levelization Training                                          |     |

|     |        | 2.8.8.8.     | ÷                                                                    |     |

|     |        | 2.8.8.8.     | 6                                                                    |     |

|     |        | 2.8.8.8.2    |                                                                      |     |

|     |        |              | DQS Receiver Enable Training                                         |     |

|     |        | 2.8.8.8.3    | DQS Position Training                                                | 102 |

| 2.8.8.8.4 ECC Byte Lane Training                              | . 103 |

|---------------------------------------------------------------|-------|

| 2.8.8.8.5 Calculating MaxRdLatency                            | . 104 |

| 2.8.8.8.5.1 MaxRdLatency Training                             | . 105 |

| 2.8.8.6 Continuous Pattern Generation                         | . 106 |

| 2.8.9 Memory Interleaving Modes                               | 107   |

| 2.8.9.1 Chip Select Interleaving                              | . 107 |

| 2.8.9.2 Node Interleaving                                     |       |

| 2.8.10 Memory Hoisting.                                       |       |

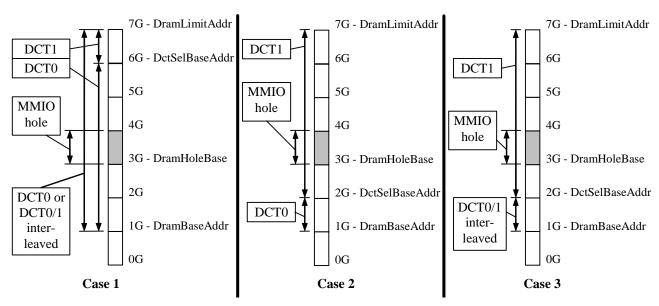

| 2.8.10.1 DramHoleOffset Programming                           |       |

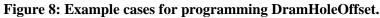

| 2.8.10.2 DctSelBaseOffset Programming                         |       |

| 2.8.11 On-Line Spare                                          | 112   |

| 2.8.11.1 On-Line Spare and CS Interleaving                    |       |

| 2.9 CPU Core.                                                 |       |

| 2.9.1 Virtual Address Space                                   |       |

| 2.9.2 CPU Cores and Downcoring                                |       |

| 2.9.3 Access Type Determination.                              |       |

| 2.9.3.1 Memory Access to the Physical Address Space           |       |

| 2.9.3.1.1 Determining The Cache Attribute                     |       |

| 2.9.3.1.2 Determining The Access Destination for CPU Accesses |       |

| 2.9.4 Timers                                                  |       |

| 2.9.5 APIC                                                    |       |

| 2.9.5.1 ApicId Enumeration Requirements                       |       |

| 2.10 Thermal Functions.                                       |       |

| 2.10.1 The Tctl Temperature Scale.                            |       |

| 2.10.2 Thermal Diode                                          |       |

| 2.10.3 Temperature-Driven Logic                               |       |

| 2.10.3.1 PROCHOT_L and Hardware Thermal Control (HTC)         |       |

| 2.10.3.2 Software Thermal Control (STC)                       |       |

| 2.10.3.3 THERMTRIP                                            |       |

| 2.11 Configuration Space                                      |       |

| 2.11.1 MMIO Configuration Coding Requirements.                |       |

| 2.11.2 MMIO Configuration Ordering                            |       |

| 2.11.3 Processor Configuration Space                          |       |

| 2.12 . RAS and Advanced Server Features                       |       |

| 2.12.1 Machine Check Architecture                             |       |

| 2.12.1.1 Machine Check Registers                              | . 120 |

| 2.12.1.2 Machine Check Errors                                 |       |

| 2.12.1.2.1 Machine Check Error Logging and Reporting          |       |

| 2.12.1.2.2 Error Overflow                                     |       |

| 2.12.1.3 MCA Initialization                                   |       |

| 2.12.1.4 Handling Machine Check Exceptions                    |       |

| 2.12.1.5 Error Diagnosis                                      |       |

| 2.12.1.5.1 Common Diagnosis Information                       |       |

| 2.12.1.6 Error Thresholding                                   |       |

| 2.12.1.7 Scrub Rate Recommendations                           |       |

| 2.12.1.8 Error Injection and Simulation                       |       |

| 2.12.2 DRAM Considerations for ECC.                           |       |

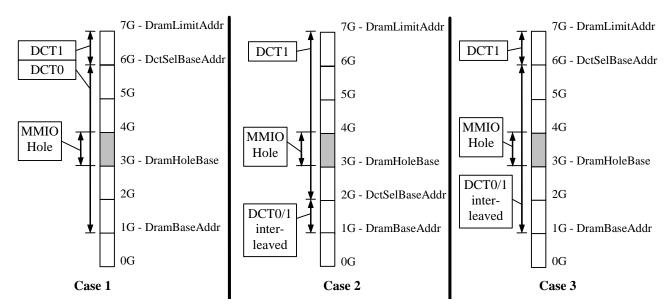

| 2.12.2.1 Multi-Beat Interleaving for Unganged Mode            |       |

| 2.12.2.2 ECC Syndromes                                        |       |

| 2.12.3 Sideband Interface (SBI)                               |       |

|                                                               |       |

| 2.12.3.1 SBI Processor Information                                            | . 131 |

|-------------------------------------------------------------------------------|-------|

| 2.13 Interrupts                                                               | 131   |

| 2.13.1 Local APIC                                                             | 131   |

| 2.13.1.1 Physical Destination Mode                                            | . 131 |

| 2.13.1.2 Logical Destination Mode                                             | . 132 |

| 2.13.1.3 Interrupt Delivery                                                   | . 132 |

| 2.13.1.4 Vectored Interrupt Handling                                          | . 132 |

| 2.13.1.5 Interrupt Masking                                                    |       |

| 2.13.1.6 Spurious Interrupts                                                  |       |

| 2.13.1.6.1 Spurious Interrupts Caused by Timer Tick Interrupt                 | . 133 |

| 2.13.1.7 Lowest-Priority Interrupt Arbitration                                |       |

| 2.13.1.8 Inter-Processor Interrupts                                           |       |

| 2.13.1.9 APIC Timer Operation                                                 |       |

| 2.13.1.10 Generalized Local Vector Table                                      |       |

| 2.13.1.11 State at Reset                                                      |       |

| 2.13.2 System Management Mode (SMM)                                           |       |

| 2.13.2.1 SMM Overview                                                         |       |

| 2.13.2.2 Operating Mode and Default Register Values                           |       |

| 2.13.2.3 SMI Sources And Delivery                                             |       |

| 2.13.2.4 SMM Initial State                                                    |       |

| 2.13.2.5 SMM Save State                                                       |       |

| 2.13.2.6 Exceptions and Interrupts in SMM                                     |       |

| 2.13.2.7 The Protected ASeg and TSeg Areas                                    |       |

| 2.13.2.8 SMM Special Cycles                                                   |       |

| 2.13.2.9 Locking SMM                                                          |       |

| 2.13.2.10 Multiple Unsynchronized SMI Sources                                 |       |

| 2.14 Secure Virtual Machine Mode (SVM)                                        |       |

| 2.14.1 BIOS support for SVM Disable.                                          |       |

| 2.15 CPUID Instruction.                                                       |       |

| 2.15.1 Multi-Core Support                                                     |       |

| 2.15.2 L3 Cache Support                                                       |       |

| 2.16 Performance Monitoring                                                   |       |

| 2.16.1 Performance Monitor Counters                                           |       |

| 2.16.2 Instruction Based Sampling (IBS).                                      |       |

|                                                                               |       |

| 8                                                                             | 147   |

| 3.1 Register Descriptions and Mnemonics                                       | 147   |

| 3.1.1 Northbridge MSRs In Multi-Core Products                                 | 148   |

| 3.2 IO Space Registers.                                                       | 148   |

| 3.3 Function 0 HyperTransport <sup>™</sup> Technology Configuration Registers | 149   |

| 3.4 Function 1 Address Map Registers                                          | 169   |

| 3.5 Function 2 DRAM Controller Registers                                      | 178   |

| 3.6 Function 3 Miscellaneous Control Registers.                               | 222   |

| 3.7 Function 4 Link Control Registers                                         | 275   |

| 3.8 APIC Registers                                                            | 294   |

| 3.9 CPUID Instruction Registers                                               | 304   |

| 3.10 MSRs - MSR0000_xxxx                                                      | 312   |

| 3.11 MSRs - MSRC000_0xxx                                                      | 331   |

| 3.12 MSRs - MSRC001_0xxx                                                      | 333   |

| 3.13 MSRs - MSRC001_1xxx                                                      | 352   |

| 2 | 3.14 Performance Counter Events                | 59 |

|---|------------------------------------------------|----|

|   | 3.14.1 Floating Point Events                   | 59 |

|   | 3.14.2 Load/Store and TLB Events               | 51 |

|   | 3.14.3 Data Cache Events                       | 52 |

|   | 3.14.4 L2 Cache and System Interface Events 36 |    |

|   | 3.14.5 Instruction Cache Events                |    |

|   | 3.14.6 Execution Unit Events                   |    |

|   | 3.14.7 Memory Controller Events 37             | 74 |

|   | 3.14.8 Crossbar Events                         |    |

|   | 3.14.9 Link Events                             | 32 |

|   | 3.14.10 L3 Cache Events                        | 32 |

| 4 | Register List                                  | 34 |

# **List of Figures**

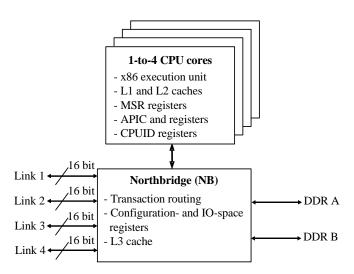

| Figure 1:  | A processor                                                     |    |

|------------|-----------------------------------------------------------------|----|

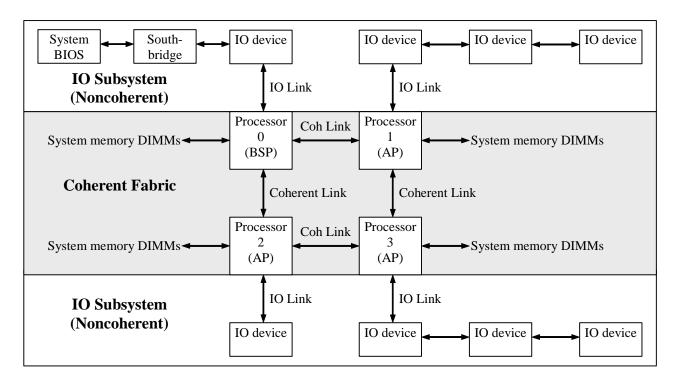

| Figure 2:  | System diagram                                                  |    |

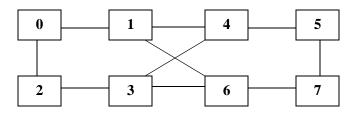

| Figure 3:  | Example 8 node system in twisted ladder topology                |    |

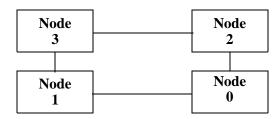

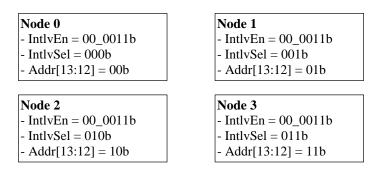

| Figure 4:  | Sample four-node configuration                                  | 66 |

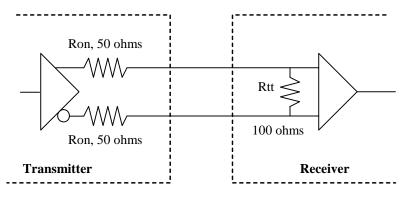

| Figure 5:  | Link DC termination mode.                                       |    |

| Figure 6:  | DDR3 x8 Registered DIMM                                         |    |

| Figure 7:  | DDR3 Registered x4 DIMM (planar)                                |    |

| Figure 8:  | Example cases for programming DramHoleOffset                    |    |

| Figure 9:  | Example cases for programming DctSelBaseOffset                  |    |

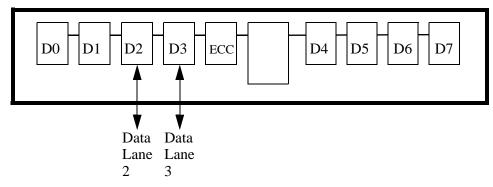

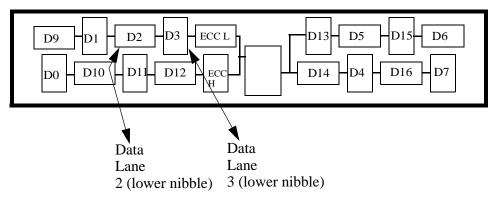

| Figure 10: | Example of line interleaving from x4 DRAM in unganged DRAM mode |    |

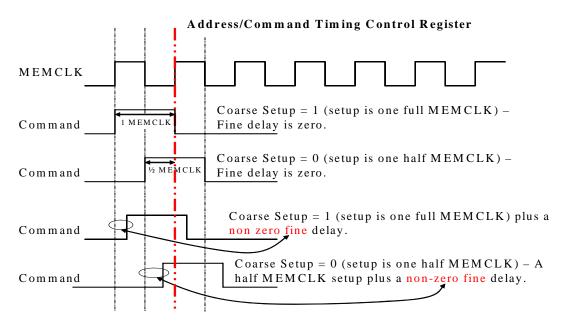

| Figure 11: | Address/Command Timing at the Processor Pins                    |    |

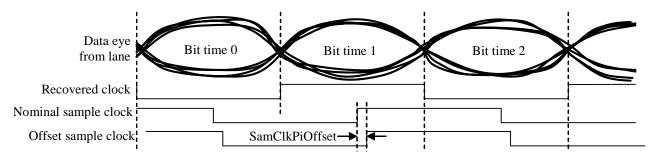

| Figure 12: | Link phy recovered clock and sample clock                       |    |

|            |                                                                 |    |

# **List of Tables**

| Table 1:  | Processor revision conventions                                                    | 23  |

|-----------|-----------------------------------------------------------------------------------|-----|

| Table 2:  | Supported feature variations by revision                                          | 27  |

| Table 3:  | SLIT table example                                                                | 33  |

| Table 4:  | Power management support                                                          | 34  |

| Table 5:  | Boot VID codes                                                                    | 37  |

| Table 6:  | PVI VID codes                                                                     | 37  |

| Table 7:  | SVI and internal VID codes                                                        | 38  |

| Table 8:  | Representative mixed frequency P-state table example (step 2)                     | 50  |

| Table 9:  | Representative mixed frequency P-state table example (step 3)                     |     |

| Table 10: | Representative mixed frequency P-state table example (step 4)                     | 51  |

| Table 11: | Representative mixed frequency P-state table example (step 6)                     | 52  |

| Table 12: | Representative mixed frequency P-state table example (step 7)                     | 53  |

| Table 13: | Representative mixed frequency P-state table example (final)                      | 54  |

| Table 14: | Representative mixed frequency _PSS object example                                | 54  |

| Table 15: | Link disconnect controls                                                          | 71  |

| Table 16: | Supported link operational modes                                                  | 73  |

| Table 17: | DDR2 Unbuffered and Registered Maximum Frequency Support (per channel)            | 74  |

| Table 18: | DDR3 Unbuffered Maximum Frequency Support (per channel)                           | 75  |

| Table 19: | DDR2 Four Bank Activate Window Values                                             | 83  |

| Table 20: | ODT Settings for DDR2 Unbuffered and Registered DIMMs                             | 83  |

| Table 21: | ODT Settings for DDR3 Unbuffered DIMMs (2 DIMMs per channel)                      | 84  |

| Table 22: | DDR3 Unbuffered DIMM Write Leveling ODT Pattern                                   | 85  |

| Table 23: | DDR2 Unbuffered DIMM Address Timings and Drive Strengths                          | 86  |

| Table 24: | DDR2 Registered DIMM Address Timings and Drive Strengths (4 DIMMs per channel)    | 87  |

| Table 25: | DDR2 Registered DIMM Address Timings and Drive Strengths (2 DIMMs per channel)    | 87  |

| Table 26: | DDR3 Unbuffered DIMM Address Timings and Drive Strengths                          | 88  |

| Table 27. | DDR3 RDIMM Register Control Word Values                                           | 95  |

| Table 28. | DDR2 swapped normalized address lines for interleaving for a 64-bit interface     | 108 |

| Table 29. | DDR2 swapped normalized address lines for CS interleaving for a 128-bit interface | 108 |

| Table 30. | DDR3 swapped normalized address lines for interleaving for a 64-bit interface     | 109 |

| Table 31. | DDR3 swapped normalized address lines for CS interleaving for a 128-bit interface | 109 |

| Table 32: | MCA register cross-reference table                                                | 120 |

| Table 33: | MC0 and MC4 Overwrite Priorities                                                  | 122 |

| Table 34: | MC1, MC2, MC3, and MC5 Overwrite Priorities                                       | 122 |

| Table 35: | MCA Registers Commonly Used for Diagnosis                                         | 125 |

| Table 36: | ECC correctable syndromes                                                         | 130 |

| Table 37: | SMM initial state                                                                 | 136 |

| Table 38: | SMM Save State                                                                    | 136 |

| Table 39: | Terminology in register descriptions                                              | 147 |

| Table 40: | DIMM support per package                                                          | 179 |

| Table 41: | Logical DIMM, Chip Select, CKE, ODT, and Register Mapping      |  |

|-----------|----------------------------------------------------------------|--|

| Table 42: | DDR2 DRAM address mapping                                      |  |

| Table 43: | DDR3 DRAM address mapping                                      |  |

| Table 44: | Error codes: transaction type                                  |  |

| Table 45: | Error codes: cache level                                       |  |

| Table 46: | Error codes: memory transaction type                           |  |

| Table 47: | Error codes: participation processor                           |  |

| Table 48: | Error codes: memory or IO                                      |  |

| Table 49: | NB error descriptions                                          |  |

| Table 50: | NB error signatures, part 1                                    |  |

| Table 51: | NB error signatures, part 2                                    |  |

| Table 52: | Default MCA NB Address Register default encoding               |  |

| Table 53: | MCA NB Address Low Register encoding Protocol Errors           |  |

| Table 54: | MCA NB Address Low Register encoding for NB Array Errors       |  |

| Table 55: | MCA NB Address Register encoding for L3 Array Errors           |  |

| Table 56: | MCA NB Address Low Register encoding for Watchdog Timer Errors |  |

| Table 57: | ACPI Power State Control Register SMAF Settings                |  |

| Table 58: | Valid ICR field combinations                                   |  |

| Table 59: | DC error descriptions                                          |  |

| Table 60: | DC error signatures                                            |  |

| Table 61: | DC error data; address register                                |  |

| Table 62: | IC error descriptions                                          |  |

| Table 63: | IC error signatures                                            |  |

| Table 64: | IC error data; address register                                |  |

| Table 65: | BU error descriptions                                          |  |

| Table 66: | BU error signatures                                            |  |

| Table 67: | BU error data; address register                                |  |

| Table 68: | LS error signatures                                            |  |

| Table 69: | FR error signatures                                            |  |

# **Revision History**

#### **Revision 3.18 To Revision 3.20 Changes**

- Updated 2.4.2.11.4 [\_PSD (P-State Dependency)].

- Clarified 2.4.2.13.3 [NB COF and VID Transition Sequence After Warm Reset].

- Updated or added the following sections to include support for AM3 dual-plane only processors:

- 2.4.2.5 [BIOS Requirements for P-State Initialization and Transitions].

- 2.4.2.6 [BIOS Configuration for Dual-plane Only Support].

- 2.4.2.7.1 [BIOS NB COF and VID Configuration for SVI and Single-Plane PVI Systems].

- 2.4.2.7.2 [BIOS NB COF and VID Configuration for Dual-Plane PVI Systems]

- Clarified 2.4.2.11.2 [\_PSS (Performance Supported States)] and F3xD4[PowerStepUp].

- Updated 2.7.7 [LDTSTOP Requirements].

- Updated Table 16.

- Clarified F0x[F0, D0, B0, 90][LockBc].

- Clarified F0x[14C:130][RetryModeEn] and F0x[18C:170][ScrambleEn].

- Clarified F2x[1, 0]94[ProcOdtDis].

- Clarified F3x58.

- Updated F3x74.

- Updated F3xD8[TdpVid].

- Added F3x1FC[DualPlaneOnly].

- Added EventSelect 1CFh.

- Clarified EventSelect 0F6h.

#### **Revision 3.06 To Revision 3.18 Changes**

- Initial public release for revision C.

- Clarified F2x[1, 0]88[MemClkDis].

- Clarified F2x[1, 0]9C\_x[3:0]0[2:1], F2x[1, 0]9C\_x[3:0]0[6:5], and F2x[1, 0]9C\_x[4A:30].

- Updated F3xA0[PllLockTime].

- Updated 2.7.10 [Miscellaneous Behaviors and Requirements].

- Updated 2.8.8.5.1 [Software DDR2 Device Initialization].

- Updated 2.12.1.5.1 [Common Diagnosis Information].

- Updated F0x[F0, D0, B0, 90], F3x6C, F3x74, and F3x140.

- Clarified F2x[1, 0][5C:40][TestFail].

- Clarified MSR0000\_017B.

- Updated CPUID Fn0000\_0001\_ECX[31].

- Clarified 2.3.1 [BSP initialization] and 2.3.2 [AP initialization].

- Updated 2.4.2.11.4 [\_PSD (P-State Dependency)].

- Updated 2.8.8.4.7 [DRAM ODT Control].

- Corrected 2.8.8.5.1 [Software DDR2 Device Initialization].

- Updated 2.8.8.8.1 [Write Levelization Training].

- Updated 2.8.8.8.2 [DQS Receiver Enable Training].

- Corrected 2.8.8.4 [ECC Byte Lane Training].

- Updated 2.12.1.2.1 [Machine Check Error Logging and Reporting].

- Added 2.12.1.3 [MCA Initialization].

- Updated F0x16C[ForceFullT0].

- Clarified F0x[18C:170][LS2En].

- Clarified F1x[BC:80].

- Updated F2x[1, 0]78[MaxRdLatency].

- Clarified F2x[1, 0]94[Ddr3Mode].

- Updated F3x5C[ScrubAddrLo] and F3x60[ScrubAddrHi].

- Updated F3x1[78, 70, 68, 60][IntType].

- Updated EventSelect 165h.

- Updated F2x[1, 0]90[PendRefPayback].

- Updated F2x[1, 0]9C\_x08[WrLvOdt].

- Clarified F3x58.

- Updated Table 23.

- Updated Table 26.

- Updated 2.8.8.5.1 [Software DDR2 Device Initialization].

- Clarified Table 38.

- Clarified F0x150.

- Updated F2x[1, 0]98.

- Updated F2x[1, 0]9C\_x[3:0]0[6:5].

- Updated MSRC001\_00[68:64][NbDid].

- Clarified MSRC001\_1037[IbsDcMissLat].

- Clarified EventSelect 0CBh.

- Updated 2.4.1.4 [PSI\_L].

- Updated 2.5.1 [ACPI Power State Transitions].

- Updated 2.8.8.4.7 [DRAM ODT Control].

- Updated 2.12.1.4 [Handling Machine Check Exceptions].

- Clarified F3x44[GenCrcErrByte1, GenCrcErrByte0].

- Updated F4x1[9C, 94, 8C, 84]\_x[DF, CF].

- Updated MSR0000\_0400.

- Updated MSRC000\_0081 to MSRC000\_0102 reset values.

- Clarified MSR0000\_0401[CECC, UECC], Table 59, Table 60.

- Clarified 2.8.8.5 [DRAM Device and Controller Initialization].

- Clarified 2.2.1 [Mixed Stepping].

- Updated 2.4.1.4 [PSI\_L].

- Clarified 2.4.3 [C-states].

- Updated 2.5.1 [ACPI Power State Transitions].

- Clarified 2.6.4.2.4 [Display Refresh And IFCM].

- Updated 2.8.8.5.2.1 [Software Control Word Initialization] and Table 27

- Clarified 2.9.3.1.2 [Determining The Access Destination for CPU Accesses].

- Clarified 2.12.1.4 [Handling Machine Check Exceptions].

- Clarified 2.12.2.1 [Multi-Beat Interleaving for Unganged Mode].

- Clarified F0x[F0, D0, B0, 90].

- Clarified F0x150.

- Updated F1x110.

- Corrected F1x114\_x2.

- Clarified F3x1A0[L3FreeListCBC].

- Clarified MSRC001\_0015[TlbCacheDis].

- Clarified MSRC001\_00[49:44].

- Updated 2.7.10 [Miscellaneous Behaviors and Requirements].

- Updated 2.8.8.8.1.2 [Write Leveling Seed Value].

- Corrected 2.8.8.8.3 [DQS Position Training].

- Corrected 2.8.8.8.4 [ECC Byte Lane Training].

- Clarified F2x[1, 0]84[PchgPDModeSel].

- Updated F2x[1, 0]88[Tcl].

- Updated F2x[1, 0]8C[Trdrd, TrwtTO].

- Clarified F2x[1, 0]90[ForceAutoPchg]

- Clarified F2x[1, 0]94[PowerDownMode, FourRankRDimm, DisDramInterface, ZqcsInterval].

- Corrected F2x[1, 0]98[DctAccessWrite].

- Corrected F2x[1, 0]9C\_x04.

- Updated F2x[1, 0]9C\_x08[DisAutoComp].

- Clarified F3xB0[BadDramCs0, SwapEn0].

- Clarified F3xF8\_x4[MceEn].

- Updated 2.3.3 [Using L2 Cache as General Storage During Boot].

- Updated 2.4.2.3 [P-state Bandwidth Requirements].

- Updated 2.7.7 [LDTSTOP Requirements].

- Updated Table 17.

- Corrected Table 25.

- Corrected 2.8.8 [DCT/DRAM Initialization], 2.8.8.8.1 [Write Levelization Training], and 2.8.8.8.1.2 [Write Leveling Seed Value].

- Clarified 2.12.1.7 [Scrub Rate Recommendations].

- Updated F0x68[BufRelPri].

- Updated F0x150 recommended values.

- Updated F0x16C[InLnSt].

- Updated F0x[18C:170][ILMEn, BistEn, LS2En].

- Corrected F2x[1, 0]94[PowerDownMode].

- Corrected F2x[1, 0]9C\_x00[ClkDrvStren].

- Updated F4x1[9C, 94, 8C, 84]\_x[D4, C4].

- Clarified MSRC001\_0015[LimitCpuidStdMaxVal].

- Clarified MSRC001\_1036[NbIbsReqDstProc] and MSRC001\_1037[IbsDcMabHit].

- Clarified EventSelect 067h.

- Updated 2.7.1.2 [Ganging Detection And Control].

- Clarified 2.8.7 [DRAM Data Burst Mapping].

- Added 2.13.2.10 [Multiple Unsynchronized SMI Sources].

- Clarified F2x[1, 0]7C[SendMrsCmd].

- Clarified F3xD4[PowerStepUp].

- Corrected APIC[530:500] reset value.

- Clarified MSRC001\_1022[REQ\_CTR].

- Updated 2.4.1 [Processor Power Planes And Voltage Control].

- Clarified 2.7.10 [Miscellaneous Behaviors and Requirements].

- Corrected 2.8.5 [Routing DRAM Requests].

- Clarified 2.8.8.4 [Non-SPD ROM-Based Configuration].

- Clarified 2.8.9.1 [Chip Select Interleaving].

- Clarified F2x[1, 0][5C:40][OnDimmMirror].

- Clarified F2x[1, 0]8C[DisAutoRefresh].

- Clarified F2x[1, 0]94[BankSwizzleMode, ZqcsInterval].

- Updated F2x110[DctSelIntLvAddr].

- Clarified MSRC001\_00[68:64][NbDid].

- Added 2.4.2.8 [Processor-Systemboard Power Removal Check].

- Updated 2.4.2.13.1 [Core Maximum P-State Transition Sequence After Warm Reset].

- Updated 2.4.2.13.2 [Core Minimum P-State Transition Sequence After Warm Reset].

- Clarified 2.4.2.13.3 [NB COF and VID Transition Sequence After Warm Reset].

- Clarified 2.4.4 [ACPI Suspend to RAM State (S3)].

- Clarified 2.14.1 [BIOS support for SVM Disable].

- Updated Table 39.

- Clarified F3x44[IoRdDatErrEn, CpuRdDatErrEn].

- Clarified F3xD8[TdpVid].

- Added MSRC001\_102A[ThrottleNbInterface].

AMD Family 10h Processor BKDG

- Updated EventSelect 08Ch.

- Clarified 1.4 [Definitions].

- Clarified 2.8.8.5.2 [Software DDR3 Device Initialization].

- Updated 2.12.1.4 [Handling Machine Check Exceptions].

- Added 2.12.1.5 [Error Diagnosis].

- Clarified 2.12.1.6 [Error Thresholding]

- Updated 2.12.2 [DRAM Considerations for ECC].

- Corrected Figure 10.

- Corrected F1x[1, 0][7C:40][DramBase, IntlvEn] reset values.

- Clarified F2x[1, 0]7C[DeassertMemRstX].

- Clarified F2x[1, 0]94[DisDramInterface].

- Updated F2x[1, 0]9C\_x0C.

- Updated F3x44 and F3x180 recommendations.

- Corrected Table 49 and Table 51 PCC setting for Link Data Error.

- Clarified F3x180[DisPciCfgCpuMstAbtRsp].

- Corrected MSRC001\_00[07:04][CTR].

#### **Revision 3.00 To Revision 3.06 Changes**

- Updated MSRC001\_0070[NbDid].

- Clarified 2.4.4 [ACPI Suspend to RAM State (S3)].

- Clarified 2.8.8.5 [DRAM Device and Controller Initialization].

- Clarified 2.8.8.5.1 [Software DDR2 Device Initialization].

- Clarified 2.8.8.5.2 [Software DDR3 Device Initialization].

- Updated 2.8.8.7 [DRAM Channel Frequency Change].

- Corrected 2.9.3.1.2 [Determining The Access Destination for CPU Accesses].

- Clarified F2x[1, 0]7C[EnDramInit].

- Clarified F2x[1, 0]9C\_x04 programming requirements.

- Clarified F3x44[DisPciCfgCpuErrRsp].

- Clarified F3x180[DisPciCfgCpuMstAbtRsp].

- Clarified 2.4.2.10.2 [Mixed Frequency and Power P-State Configuration Rules].

- Updated 2.4.2.10.3 [Mixed Frequency and Power P-State Configuration Sequence].

- Updated 2.4.2.13.1 [Core Maximum P-State Transition Sequence After Warm Reset].

- Updated 2.4.2.13.2 [Core Minimum P-State Transition Sequence After Warm Reset].

- Clarified 2.6.6 [Memory Scrubbers].

- Added 2.12.1.7 [Scrub Rate Recommendations].

- Clarified 2.12.2 [DRAM Considerations for ECC].

- Clarified F3x40[UECC, CECC].

- Clarified F3x4C.

- Clarified F3x58.

- Clarified MSRC001\_0015[McStatusWrEn].

- Added BSC to 1.4 [Definitions].

- Clarified 2.3 [Processor Initialization].

- Clarified 2.4.2.10.2 [Mixed Frequency and Power P-State Configuration Rules].

- Updated 2.4.2.13.2 [Core Minimum P-State Transition Sequence After Warm Reset].

- Updated 2.4.4 [ACPI Suspend to RAM State (S3)].

- Clarified F2x[1, 0]94[PowerDownMode].

- Updated F3xD8[VSSlamTime].

- Clarified F3xF0.

- Updated CPUID Fn8000\_0006[ECX].

- Updated 2.8.8.1 [Phy and Controller Mode Configuration].

- Clarified 2.13.1 [Local APIC].

- Clarified 2.13.1.11 [State at Reset].

- Updated F3x44[WDTBaseSel].

- Added F3x1EC\_x[FF:01].

- Updated F4x1[9C, 94, 8C, 84]\_x[D4, C4].

- Clarified APICF0[APICSWEn].

- Clarified MSR0000\_001B[ApicEn].

- Updated EventSelect 0E0h.

- Added TDP to 1.4 [Definitions].

- Updated Table 2.

- Updated 2.3.3 [Using L2 Cache as General Storage During Boot].

- Updated 2.7.10 [Miscellaneous Behaviors and Requirements].

- Updated 2.8.8.2 [Phy compensation initialization].

- Clarified RDQS in 2.8.8.5.1 [Software DDR2 Device Initialization].

- Clarified TDQS in 2.8.8.5.2 [Software DDR3 Device Initialization].

- Updated 2.8.8.8.2 [DQS Receiver Enable Training].

- Updated 2.8.8.8.3 [DQS Position Training].

- Clarified 2.9.2 [CPU Cores and Downcoring].

- Updated 2.12.1.6 [Error Thresholding]

- Updated 2.12.2 [DRAM Considerations for ECC].

- Updated F0x16C[ForceFullT0] BIOS recommendation.

- Clarified F2x[1, 0]88[Trtp].

- Clarified F2x[1, 0]94[RDqsEn].

- Updated F2x[1, 0]9C\_x[3:0]0[2:1] and F2x[1, 0]9C\_x[3:0]03.

- Updated F2x[1, 0]9C\_x[3:0]0[6:5] and F2x[1, 0]9C\_x[3:0]07.

- Clarified F3xD4.

- Added F3xD8[TdpVid].

- Updated F3x1[78, 70, 68, 60].

- Clarified MSR0000\_0410, MSR0000\_0411, MSR0000\_0412.

- Updated MSR0000\_0413.

- Added MSRC001\_001F[DisXdsBypass].

- Clarified MSRC001\_102A[ClLinesToNbDis].

- Added MSRC001\_102A[FrcWTMemTypToWPDis].

- Updated 1.5.2 [Major Changes Relative to Family 0Fh Processors].

- Updated 2.4.1 [Processor Power Planes And Voltage Control].

- Clarified 2.4.2 [P-states].

- Updated 2.4.2.7.1 [BIOS NB COF and VID Configuration for SVI and Single-Plane PVI Systems].

- Updated 2.4.2.13.1 [Core Maximum P-State Transition Sequence After Warm Reset].

- Updated F0x[E4, C4, A4, 84][LdtStopTriEn].

- Updated F3xE8[MpCap].

- Clarified APIC340 behavior.

- Updated F2x11C[MctPrefReqLimit] and F3x78[RspDBC] requirements.

- Updated MSRC001\_0114 field definitions.

- Updated 1.2 [Reference Documents].

- Updated 2.3.3 [Using L2 Cache as General Storage During Boot].

- Clarified 2.4.2.10.2 [Mixed Frequency and Power P-State Configuration Rules].

- Clarified 2.4.2.11 [ACPI Processor P-State Objects].

- Updated 2.4.4 [ACPI Suspend to RAM State (S3)].

- Clarified F2x11C recommendation to enable prefetcher.

- Updated Table 57 C1E setting.

- Updated MSRC001\_102A[ClLinesToNbDis].

- Added IOMMU to 1.4 [Definitions].

- Updated 2.4.2.9 [Processor-Systemboard Power Delivery Compatibility Check].

- Updated Table 21.

- Updated 2.8.8.8.5.1 [MaxRdLatency Training].

- Updated 2.8.11 [On-Line Spare].

- Updated 2.9.3.1.2 [Determining The Access Destination for CPU Accesses] with programming notes for cacheable IO.

- Updated 2.12.1.6 [Error Thresholding].

- Updated Table 39. Added Write-only attribute.

- Added F2x[1, 0]78[ChSetupSync].

- Updated F3x40[ProtEn].

- Updated Table 49 Protocol Error.

- Updated Table 50 and Table 51 with combined link and L3 protocol errors.

- Corrected Table 51: L3 Cache LRU Error/Syndrome Valid.

- Updated Table 53 with contents of table MCA NB Address Low Register encoding for L3 Protocol Errors

- Clarified F3x140 IsocPreqTok requirements for display refresh mode.

- Updated F3x180[SnycOnProtEn].

- Added F3x1FC[SinglePlaneNbIdd].

- Updated F4x1[98, 90, 88, 80][LinkPhyOffset] to be 10 bits

- Added MSR0000\_02FF[MtrrDefTypeFixEn] access rule.

- Added NBC, XBAR, and updated WDT in 1.4 [Definitions].

- Added 2.3.6 [SLIT and SRAT].

- Updated 2.6.2 [The GART].

- Updated 2.8.5 [Routing DRAM Requests].

- Added 2.8.6 [DRAM Controller Direct Response Mode].

- Updated 2.8.7 [DRAM Data Burst Mapping].

- Updated 2.8.8.4.1 [Trdrd (Read to Read Timing)].

- Updated 2.8.8.4.2 [Twrwr (Write to Write Timing)].

- Updated 2.8.8.4.3 [Twrrd (Write to Read DIMM Termination Turn-around)].

- Updated 2.8.8.4.4 [TrwtTO (Read-to-Write Turnaround for Data, DQS Contention)].

- Added MC5 to 2.12.1.2.2 [Error Overflow], and to Table 34.

- Added 2.12.1.8 [Error Injection and Simulation].

- Updated 2.13.1.3 [Interrupt Delivery] with sentence from 2.13.1.3 [Interrupt Delivery].

- Clarify effect of F3x44[NbMcaToMstCpuEn] in multi-core processors.

- Updated Table 49 on page 231.

- Updated Table 56 on page 239.

- Updated F4x1[9C, 94, 8C, 84]\_x[D5, C5] description with how to determine the appropriate deemphasis setting.

- Updated APIC[1F0:180][TriggerModeBits] description.

#### **Revision 3.00**

• Initial public release.

# 1 Overview

The AMD family 10h processor (in this document referred to as *the processor*) is a processing unit that supports x86-based instruction sets. The processor includes (a) up to four independent central processing unit cores (referred to as *cores*), (b) up to four high-speed communication interfaces (referred to as *links*) that may be configured for HyperTransport<sup>TM</sup> technology (referred to as *IO links*) or for AMD-proprietary inter-processor communication (referred to as *coherent links*), and (c) up to two double-data rate 2 (DDR2) or 3 (DDR3) system memory DRAM interfaces.

AMD family 10h processors are distinguished by the combined ExtFamily and BaseFamily fields of the CPUID instruction (see CPUID Fn[8000\_0001, 0000\_0001]\_EAX in section 3.9 [CPUID Instruction Registers]).

#### 1.1 Intended Audience

This document provides the processor behavioral definition and associated design notes. It is intended for platform designers and for programmers involved in the development of low-level BIOS (basic input/output system) functions, drivers, and operating system kernel modules. It assumes prior experience in personal computer platform design, microprocessor programming, and legacy x86 and AMD64 microprocessor architecture. The reader should also have familiarity with various platform technologies, such as DDR DRAM.

# **1.2 Reference Documents**

- Advanced Configuration and Power Interface (ACPI) Specification. www.acpi.info.

- AMD64 Architecture Programmer's Manual Volume 1: Application Programming, #24592.

- AMD64 Architecture Programmer's Manual Volume 2: System Programming, #24593.

- AMD64 Architecture Programmer's Manual Volume 3: Instruction-Set Reference, #24594.

- AMD64 Architecture Programmer's Manual Volume 4: 128-Bit Media Instructions, #26568.

- AMD64 Architecture Programmer's Manual Volume 5: 64-Bit Media and x87 Floating-Point Instructions, #26569.

- CPUID Specification, #25481.

- AMD Socket F (1207) Processor Functional Data Sheet, #31118.

- AMD Socket Fr2 (1207) Processor Functional Data Sheet, #41698.

- AMD Socket Fr5 (1207) Processor Functional Data Sheet, #45602.

- AMD Socket AM2 Processor Functional Data Sheet, #31117.

- AMD Socket AM2r2 Processor Functional Data Sheet, #41697.

- AMD Socket AM3 Processor Functional Data Sheet, #40778.

- AMD Family 10h Processor Electrical Data Sheet, #40014.

- Revision Guide for AMD Family 10h Processors, #41322

- AMD Voltage Regulator Specification, #40182.

- AMD I/O Virtualization Technology (IOMMU) Specification, #34434.

- HyperTransport<sup>™</sup> I/O Link Specification. www.hypertransport.org.

- PCI local bus specification. www.pcisig.org.

- System Management Bus (SMBus) specification. www.smbus.org.

- SBI Temperature Sensor Interface (SB-TSI) Specification, #40821.

# 1.3 Conventions

# 1.3.1 Numbering

- Binary numbers. Binary numbers are indicated by appending a "b" at the end, e.g., 0110b.

- **Decimal numbers**. Unless specified otherwise, all numbers are decimal. Note: this rule does not apply to the register mnemonics described in section 3.1 [Register Descriptions and Mnemonics]; register mnemonics all utilize hexadecimal numbering.

- Hexadecimal numbers. hexadecimal numbers are indicated by appending an "h" to the end, e.g., 45f8h.

- Underscores in numbers. Underscores are used to break up numbers to make them more readable. They do not imply any operation. E.g., 0110\_1100b.

# 1.3.2 Arithmetic And Logical Operators

In this document, formulas follow some Verilog conventions for logic equations.

- {} Curly brackets are used to indicate a group of bits that are concatenated together. Each set of bits is separated by a comma. E.g., {Addr[3:2], Xlate[3:0]} represents a 6-bit value; the two MSBs are Addr[3:2] and the four LSBs are Xlate[3:0].

- Logical OR operator.

- & Logical AND operator.

- A Logical exclusive-OR operator; sometimes used as "raised to the power of" as well, as indicated by the context in which it is used.

- ~ Logical NOT operator.

- == Logical "is equal to" operator.

- != Logical "is not equal to" operator.

- <= Less than or equal operator.

- >= Greater than or equal operator.

- \* Arithmetic multiplied-by operator.

The order in which logical operators are applied is: ~ first, & second, and | last.

#### For example, the equation:

```

Output[3:0] = {A[1:0], B[3:2]} & C[3:0] | ~D[3:0] & E[9:6],

is translated as:

Output[3] = (A[1] & C[3]) | (~D[3] & E[9]);

Output[2] = (A[0] & C[2]) | (~D[2] & E[8]);

Output[1] = (B[3] & C[1]) | (~D[1] & E[7]);

Output[0] = (B[2] & C[0]) | (~D[0] & E[6]);

```

# 1.4 Definitions

- AC coupled. Refers to the method used for link termination. See section 2.7.2 [Termination and Compensation].

- AP. Application processor. See section 2.3 [Processor Initialization].

- APML. Advanced Platform Management Link. See section 2.12.3 [Sideband Interface (SBI)].

- BCS. Base configuration space. See section 2.11 [Configuration Space].

- **BERT**. Bit error rate tester. A piece of test equipment that generates arbitrary test patterns and checks that a device under test returns them without errors.

- **BIST**. Built-in self-test. Hardware within the processor that generates test patterns and verifies that they are stored correctly (in the case of memories) or received without error (in the case of links).

- **Boot VID**. Boot voltage ID. This is the VDD and VDDNB voltage level that the processor requests from the external voltage regulator during the initial phase of the cold boot sequence.

- **BSC**. Boot strap core. Core 0 of the BSP. Specified by MSR0000\_001B[BSC].

- BSP. Boot strap processor. See section 2.3 [Processor Initialization].

- **C0**, **C1**, **C2**, **and C3**. These are ACPI-defined core power states. C0 is operational. C1 is when the core is in halt. C2 and C3 are stop-grant states. See section 2.4 [Power Management].

- C1E. C1 enhanced state. Power-savings mode that is employed when all cores of a CMP processor are in the halt state. See [The Interrupt Pending and CMP-Halt Register] MSRC001\_0055.

- **Canonical address**. An address in which the state of the most-significant implemented bit is duplicated in all the remaining higher-order bits, up to bit 63.

- Channel. See DRAM channel.

- **Channel interleaved mode**. Mode in which DRAM address space is interleaved between DRAM channels. See section 2.8.9 [Memory Interleaving Modes].

- Chipkill ECC. An error correcting code which can recover from DRAM device failures. See section 2.12.2 [DRAM Considerations for ECC].

- CMP. Chip multi-processing. Refers to processors that include multiple cores. See section 2.1 [Processor Overview].

- **Coherent fabric**. The coherent fabric includes the DRAM controllers and caches of the system. Normally, this refers to the nodes, system memory, and coherent links used for communication between the nodes. See section 2.2 [System Overview].

- Coherent link or coh link. A link configured for coherent inter-processor traffic between nodes.

- COF. Current operating frequency of a given clock domain. See section 2.4.2 [P-states].

- Cold reset. PWROK is deasserted and RESET\_L is asserted. See section 2.3 [Processor Initialization].

- CPU or CPU core. The instruction execution unit(s) of the processor. See section 2.1 [Processor Overview].

- CpuCoreNum. Specifies the core number. See section 2.9.2 [CPU Cores and Downcoring].

- **CPUID function X**. Refers to the CPUID instruction when EAX is preloaded with X. See section 3.9 [CPUID Instruction Registers].

- CS. Chip select. See F2x[1, 0][5C:40] [DRAM CS Base Address Registers].

- **DC** coupled. Refers to the method used for link termination. See section 2.7.2 [Termination and Compensation].

- **DCQ**. DRAM controller queue.

- DCT. DRAM controller. See section 2.8 [DRAM Controllers (DCTs)].

- DEV. DMA exclusion vector. See section 2.6.3 [DMA Exclusion Vectors (DEV)].

- DID. Divisor identifier. Specifies the post-PLL divisor used to reduce the COF. See section 2.4.2 [P-states].

- **Display refresh**. Traffic used for display refresh in UMA systems. See section 2.6.4.2.4 [Display Refresh And IFCM].

- Doubleword. A 32-bit value.

- Downcoring. Removal of cores. See section 2.9.2 [CPU Cores and Downcoring].

- **DRAM channel**. The part of the DRAM interface that connects to a 64-bit DIMM. For example, a processor with a 128-bit DRAM interface is said to support two DRAM channels. See section 2.8 [DRAM Controllers (DCTs)].

- **DS**. Downstream. Refers to the direction of data on a link.

- **Dual-Plane**. Refers to a processor or systemboard where VDD and VDDNB are separate and may operate at independent voltage levels. Refer to 2.4.1 [Processor Power Planes And Voltage Control].

- DW or DWORD. Doubleword. A 32-bit value.

- ECS. Extended configuration space. See section 2.11 [Configuration Space].

- EDS. Electrical data sheet. See section 1.2 [Reference Documents].

- FDS. Functional data sheet; there is one FDS for each package type. See section 1.2 [Reference Documents].

- **FID**. Frequency identifier. Specifies the PLL frequency multiplier for a given clock domain. See section 2.4.2 [P-states].

- Ganged. A link, memory channel, or voltage regulator in which all portions are controlled as one.

- Gen1. Refers to older revisions of the link specification and, in particular, link data rates from 0.4 to 2.0 GT/s. See section 2.7 [Links].

- Gen3. Refers to revision 3.00 of the link specification and, in particular, link data rates from 2.4 to 5.2 GT/s. See section 2.7 [Links].

- **#GP**. A general-protection exception.

- #GP(0). Notation indicating a general-protection exception (#GP) with error code of 0.

- GT/s. Giga-transfers per second.

- **HTC**. Hardware thermal control. See section 2.10.3.1 [PROCHOT\_L and Hardware Thermal Control (HTC)].

- **HTC-active state**. Hardware-controlled lower-power, lower-performance state used to reduce temperature. See section 2.10.3.1 [PROCHOT\_L and Hardware Thermal Control (HTC)].

- **I2C**. Protocol on which the SVI interface timing is based. See section 2.4.1 [Processor Power Planes And Voltage Control], and section 1.2 [Reference Documents].

- IBS. Instruction based sampling. See section 2.16.2 [Instruction Based Sampling (IBS)].

- **IFCM**. Isochronous flow-control mode, as defined in the *HyperTransport*<sup>™</sup> *I/O Link Specification*. See section 2.6.4.2.4 [Display Refresh And IFCM].

- **ILM**. Internal loopback mode. Mode in which the link receive lanes are connected directly to the transmit lanes of the same link for testing and characterization. See [The Link Extended Control Registers] F0x[18C:170].

- **Inactive lane**. The inactive lanes of a link are the unused upper lanes when the operating link width is lower than the maximum link width. See the *HyperTransport*<sup>TM</sup> *I/O Link Specification*.

- **IO configuration**. Access to configuration space through IO ports CF8h and CFCh. See section 2.11 [Configuration Space].

- **IO Hub**. This is the platform device that contains the bridge to the system BIOS.

- IOMMU. AMD I/O Virtualization Technology. See the AMD I/O Virtualization Technology Specification.

- IO link. A link configured for non-coherent traffic, per the HyperTransport<sup>TM</sup> I/O Link Specification.

- **IORRs**. IO range registers. See [The IO Range Registers Base (IORR\_BASE[1:0])] MSRC001\_00[18, 16].

- Isoc. Isochronous. Isochronous is defined by the link specification.

- L1 caches. The level 1 caches of the core including the instruction cache and the data cache.

- L2 cache. The level 2 cache of each core.

- L3 cache. The level 3 cache that is shared by each of the cores.

- Link. Generic term that may refer to an IO link or a coherent link.

- LINT. Local interrupt.

- Logical DIMM. Either one 64-bit DIMM or two identical DIMMs in parallel to create a 128-bit interface. See section 2.8 [DRAM Controllers (DCTs)].

- LVT. Local vector table. A collection of APIC registers that define interrupts for local events. E.g., [The Extended Interrupt [3:0] Local Vector Table Registers] APIC[530:500].

- **Master abort**. This is a PCI-defined term that is applied to transactions on other than PCI busses. It indicates that the transaction is terminated without affecting the intended target; reads return all 1's; writes are discarded; the master abort error code is returned in the response, if applicable; master abort error bits are set if applicable.

- MCQ. Memory controller queue. See section 2.6.1 [Northbridge (NB) Architecture].

- MCT. Memory controller. See section 2.6.1 [Northbridge (NB) Architecture].

- MEMCLK. Refers to the clock signals, M[B, A][3:0]\_CLK, that are driven from the processor to DDR DIMMs.

- **MMIO**. Memory-mapped input-output range. This is physical address space that is mapped to the IO functions such as the IO links or MMIO configuration. The IO link MMIO ranges are specified by [The Memory Mapped IO Base/Limit Registers] F1x[BC:80].

- **MMIO configuration**. Access to configuration space through memory space. See section 2.11 [Configuration Space].

- MOF. Maximum operating frequency of the core(s). Normally this is the core COF in P-state 0. See section

2.4.2 [P-states].

- MSR. Model specific register. The CPU includes several MSRs for general configuration and control. See section 3.10 [MSRs MSR0000\_xxxx] for the beginning of the MSR register definitions.

- MTRR. Memory-type range register. The MTRRs specify the type of memory associated with various memory ranges. See MSR0000\_00FE, MSR0000\_02[0F:00], MSR0000\_02[6F:68, 59, 58, 50], and MSR0000\_02FF.

- NB. Northbridge. The transaction routing block of the node. See section 2.1 [Processor Overview].

- NBC. Node Base Core. The lowest numbered core in the node.

- NCLK. The main Northbridge clock. The NCLK frequency is the NB COF.

- Node ID. The identifier assigned to each node, [The Node ID Register] F0x60[NodeId].

- Node. See section 2.1 [Processor Overview].

- Normalized address. Addresses used by DCTs. See section 2.6.1 [Northbridge (NB) Architecture].

- Octword. A 128-bit value.

- **ODM**. On-DIMM mirroring. See F2x[1, 0][5C:40][OnDimmMirror].

- **ODT**. On-die termination, which is applied DRAM interface signals.

- **ODTS**. DRAM On-die thermal sensor.

- **Operational frequency**. The frequency at which the processor operates. See section 2.4 [Power Management].

- PDS. Product data sheet. See section 1.2 [Reference Documents].

- **PRBS**. Pseudo-random bit sequence.

- Processor. See section 2.1 [Processor Overview].

- **PSI**. Power Status Indicator. See section 2.4.1.4 [PSI\_L].

- P-state. Performance state. See section 2.4 [Power Management].

- **PTE**. Page table entry.

- PVI. Parallel VID interface. See section 2.4.1 [Processor Power Planes And Voltage Control].

- Quadword. A 64-bit value.

- **RAS**. Reliability, availability and serviceability (industry term). See section 2.12 [. RAS and Advanced Server Features].

- RX. Receiver.

- SBI. Sideband Interface. Also referred to as APML. See section 2.12.3 [Sideband Interface (SBI)].

- Scrubber. Background memory checking logic. See section 2.6.6 [Memory Scrubbers].

- Shutdown. A state in which the affected core waits for either INIT, RESET, or NMI. When shutdown state is entered, a shutdown special cycle is sent on the IO links.

- **Single-Plane**. Refers to a processor or systemboard where VDD and VDDNB are tied together and operate at the same voltage level. Refer to 2.4.1 [Processor Power Planes And Voltage Control].

- Slam. Refers to change the voltage to a new value in one step (as opposed to stepping). See section 2.4.1.7 [Hardware-Initiated Voltage Transitions].

- SMAF. System management action field. This is the code passed from the SMC to the processors in STP-CLK assertion messages. The action taken by the processors in response to this message is specified by [The ACPI Power State Control Registers] F3x[84:80].

- **SMBus**. System management bus. Refers to the protocol on which the serial VID interface (SVI) commands and SBI are based. See section 2.4.1 [Processor Power Planes And Voltage Control], 2.12.3 [Sideband Interface (SBI)], and section 1.2 [Reference Documents].

- **SMC**. System management controller. This is the platform device that communicates system management state information to the processor through an IO link, typically the system IO hub.

- SMI. System management interrupt. See section 2.13.2.1 [SMM Overview].

- SMM. System management mode. See section 2.13.2 [System Management Mode (SMM)].

- Southbridge. Same as IO hub.

- **Speculative event**. A performance monitor event counter that counts all occurrences of the event even if the event occurs during speculative code execution.

- STC. Software thermal control. See section 2.10.3.2 [Software Thermal Control (STC)].

- **STC-active state**. Software-controlled lower-power, lower-performance state used to reduce temperature. See section 2.10.3.2 [Software Thermal Control (STC)].

- **STC thermal zone**. Temperature range which may be programmed to generate interrupts and special bus cycles. See section 2.10.3.2 [Software Thermal Control (STC)].

- Sublink. An 8-bit-or-less (CAD) block of link signals of a link; each sublink of a link may connect to a different device. See section 2.7 [Links].

- SVI. Serial VID interface. See section 2.4.1 [Processor Power Planes And Voltage Control].

- SVM. secure virtual machine. See section 2.14 [Secure Virtual Machine Mode (SVM)].

- **Sync flood**. The propagation of continuous sync packets to all links. This is used to quickly stop the transmission of potentially bad data when there are no other means to do so. See the link specification for additional information.

- TCB. Trace capture buffer.

- TCC. Temperature calculation circuit. See section 2.10 [Thermal Functions].

- Tctl. Processor temperature control value. See section 2.10.3 [Temperature-Driven Logic].

- **TDP**. Thermal design power.

- **Thermal diode**. A diode connected to the THERMDA and THERMDC pins used for thermal measurements. See section 2.10.2 [Thermal Diode].

- Token. A scheduler entry used in various Northbridge queues to track outstanding requests. See [The SRI to XCS Token Count Register] F3x140 on Page 461.

- TX. Transmitter.

- UI. Unit interval. This is the amount of time equal to one half of a clock cycle.

- Unganged. A link, memory channel, or voltage regulator in which portions are controlled separately.

- US. Upstream. Refers to the direction of data on a link.

- VDD. Main power supply to the processor core logic.

- VDDNB. Main power supply to the processor NB logic.

- VID. Voltage level identifier. See section 2.4.1 [Processor Power Planes And Voltage Control].

- Virtual CAS. The clock in which CAS is asserted for the burst, N, plus the burst length (in MEMCLKs), minus 1; so the last clock of virtual CAS = N + BL/2 1.

- VRM. voltage regulator module.

- Warm reset. RESET\_L is asserted only (while PWROK stays high). See section 2.3 [Processor Initialization].

- WDT. Watchdog timer. A timer that detects activity and triggers an error if a specified period of time expires without the activity. For example, see [The CPU Watchdog Timer Register (CpuWdTmrCfg)] MSRC001 0074 or the NB watchdog timer in [The MCA NB Control Register] F3x40.

- XBAR. Crossbar; command packet switch. See section 2.6.1 [Northbridge (NB) Architecture].

# 1.5 Changes Between Revisions and Product Variations

#### 1.5.1 Revision Conventions

The processor revision is specified by [The Family, Model, Stepping Identifiers] CPUID Fn[8000\_0001, 0000\_0001]\_EAX. This document uses a revision letter or two letter mnemonic followed by revision letter instead of specific model numbers. The following table shows the relationship between revision and model. Where applicable, the processor stepping is indicated after the revision letter. See the *Revision Guide for AMD Family 10h Processors* for additional information about revision determination.

#### Table 1: Processor revision conventions

| Revision | CPUID Fn[8000_0001, 0000_0001]_EAX[Model] |

|----------|-------------------------------------------|

| В        | 2h                                        |

| С        | 4h, 5h, and 6h                            |

#### 1.5.2 Major Changes Relative to Family 0Fh Processors

• CPU core additions:

- Support for up to 4 cores in product variations.

- High-performance (128-bit internal data path) floating point unit (per core) in product variations.

- SSE4A instructions.

- Advanced bit manipulation (ABM) instructions.

- MWAIT and MONITOR instructions.

- Misaligned SSE mode.

- Power management state invariant time stamp counter (TSC).

- Number of extended LVT interrupts in APIC increased to 4.

- Increase in the number of large TLB page entries.

- 1 Gbyte large paging supported.

- Physical address space increased to 48 bits.

- All local sources of SMIs (including sources from the cores and from the NB) are broadcast to all cores of all nodes in the system.

- Memory controller (MCT) and DRAM controllers (DCTs) additions:

- Support for DDR2/DDR3 DIMMs in product variations.

- DIMMs controlled through two independent DRAM controllers.

- Write burst and DRAM prefetching performance improvements.

- Read and write burst support, as required for DRAM training.

- Links and IO additions:

- HyperTransport<sup>™</sup> 3.00 Technology, including support for DC-coupled mode.

- Link unganging support.

- Link-defined extended address capability to support up to 64-bit IO addresses.

- Link-defined UnitID clumping.

- Link-defined error retry.

- Link-defined isochronous flow control mode.

- Link-defined INTx support.

- Support for independent ordering between requests with different non-zero SeqID values.

- RAS-related additions:

- Core disable capability.

- New error thresholding support for errors associated with links, and the L3 cache; all the thresholding registers are additionally accessible through configuration space.

- New configurable responses to link errors: data error to target abort; master abort to no error; configuration space master abort to no error; sync flood on data errors; sync flood on target aborts.

- Added another MCA bank for a CPU watchdog timer.

- MCA control mask registers control logging in addition to reporting of errors.

- Link protocol checking.

- Ability to convert machine check exceptions into vectored interrupts or SMIs.

- General Northbridge additions:

- Support for an L3 cache, shared between cores, in product variations.

- BIOS-initiated system memory clear command.

- MMIO-based access to configuration space and support for extended configuration space; this includes support for SMI traps to these accesses as well.

- Mode whereby the IO request response order matches the IO request order.

- VGA space decoding to MMIO-space mapping registers.

- Support for multiple, simultaneous GART/DEV table walks.

- Support for evenly distributed traffic in systems that connect multiple links between the same processors.

- More DEV protection domains and a larger DEV cache.

- Ability to force all IO requests to system memory (except display refresh) to probe the cache, in support

of nested paging.

- Combined link status register for all links.

- Power management:

- Simple "fire and forget" operating system interface for P-state changes.

- Separate core and Northbridge power and clock planes.

- PVI and SVI regulator interfaces.

- Support for up to 5 independent P-states for each core.

- Support for P-state limits controlled by thermal limits (HTC) or host software (STC); used to limit the P-state requested by the operating system in order to reduce power.

#### 1.5.3 Changes For Revision C

See the following references for information about changes between these revisions.

- Changes that may result in BIOS modifications.

- 2.7.1.3.1 [Unused Links].

- Table 43: support for 8Gb DDR3 devices.

- F2x[1, 0]78[EarlyArbEn].

- F2x[1, 0]9C\_x[3:0]0[2:1].

- F2x[1, 0]9C\_x[3:0]03.

- F2x[1, 0]9C\_x[3:0]0[6:5].

- F2x[1, 0]9C\_x[3:0]07.

- F2x[1, 0]9C\_x0D.

- F2x[1, 0]9C\_x[4A:30]

- F2x[1, 0]A8[DataTxFifoWrDly].

- F2x110[DctSelIntLvAddr].

- Table 57.

- F3x180[SyncFloodOnDramTempErr].

- F2x1B0.

- F3x1E4[LvtOffset].

- F3x1E8[SbiBankSel, SbiByteCnt].

- F4x1[9C, 94, 8C, 84]\_x[D5, C5][VML, MapPreToMargin, TxLs23ClkGateEn].

- F4x1[9C, 94, 8C, 84]\_x[530A, 520A][DllAnalogOkIgnore].

- F4x1C4.

- MSRC001\_102A[RdMmExtCfgQwEn].

- Other changes.

- F3x1EC[SbiRegDat3, SbiRegDat2, SbiRegDat1].

- F4x1[9C, 94, 8C, 84]\_x[D4, C4][VdcDacFine].

- F4x1[9C, 94, 8C, 84]\_x[530A, 520A][AnalogWaitTime].

- F4x1[9C, 94, 8C, 84]\_x6[9, 8]84.

- F4x1[9C, 94, 8C, 84]\_x[D1, C1][LfxMax, LfcMin].

- F4x1[9C, 94, 8C, 84]\_x[D0, C0][RttIndex, RonIndex].

- CPUID Fn[8000\_0000, 0000\_0000]\_EAX.

- CPUID Fn8000\_0001\_ECX[SKINIT, WDT].

- CPUID Fn8000\_000A[NRIPS].

- CPUID Fn8000\_0019.

- CPUID Fn8000\_001B.

- MSRC001\_1033[IbsOpCntCtl, IbsOpCurCnt].

- MSRC001\_1037[IbsDcL2tlbHit1G].

- EventSelect 041h.

- EventSelect 045h[3].

# **1.5.4** Supported Feature Variations

The following table specifies the first revision of the processor that is expected to be productized for each feature (blank entries indicate that the feature is not supported) and the first revision of the processor a feature is expected to be removed.

| Table 2: Supported feature variations by revision | Table 2: | Supported | feature | variations | by | revision |

|---------------------------------------------------|----------|-----------|---------|------------|----|----------|

|---------------------------------------------------|----------|-----------|---------|------------|----|----------|

| Feature                                                                  | First Revision          | First Revision |

|--------------------------------------------------------------------------|-------------------------|----------------|

|                                                                          | Supported               | Removed        |

| Unbuffered DDR2 DIMM interface up to 800 MT/s                            | В                       |                |

| Unbuffered DDR2 DIMM interface up to 1067 MT/s                           | В                       |                |

| Unbuffered DDR3 DIMM interface up to 1333 MT/s                           | С                       |                |

| Registered DDR2 DIMM interface up to 800 MT/s                            | В                       |                |

| Registered DDR3 DIMM interface up to 1333 MT/s                           |                         |                |

| Gen3 link and retry DC-coupled mode (coherent links)                     | С                       |                |